Architecture 2030 Workshop @ ISCA 2016

CCC report out: Read the final report here.

Video recordings: Watch the video recordings here.

About the Workshop

Over the course of 2010-2012, the computer architecture research community, with the support of the Computer Research Association’s (CRA) Computing Community Consortium (CCC), carried out a series of visioning exercises to articulate how architectural innovation will continue to impact computing systems and society at large, identify new challenges and opportunities for architecture research, and provide guidance to funding agencies on critical priorities within our discipline and how architecture innovation can further other agency objectives. These visioning activities lead to several highly influential reports, including the National Academy report The Future of Computing Performance: Game Over or Next Level? (2011) and the CCC community whitepaper 21st Century Computer Architecture (2012). These community-driven efforts contributed to the establishment of funding programs and new major research efforts.

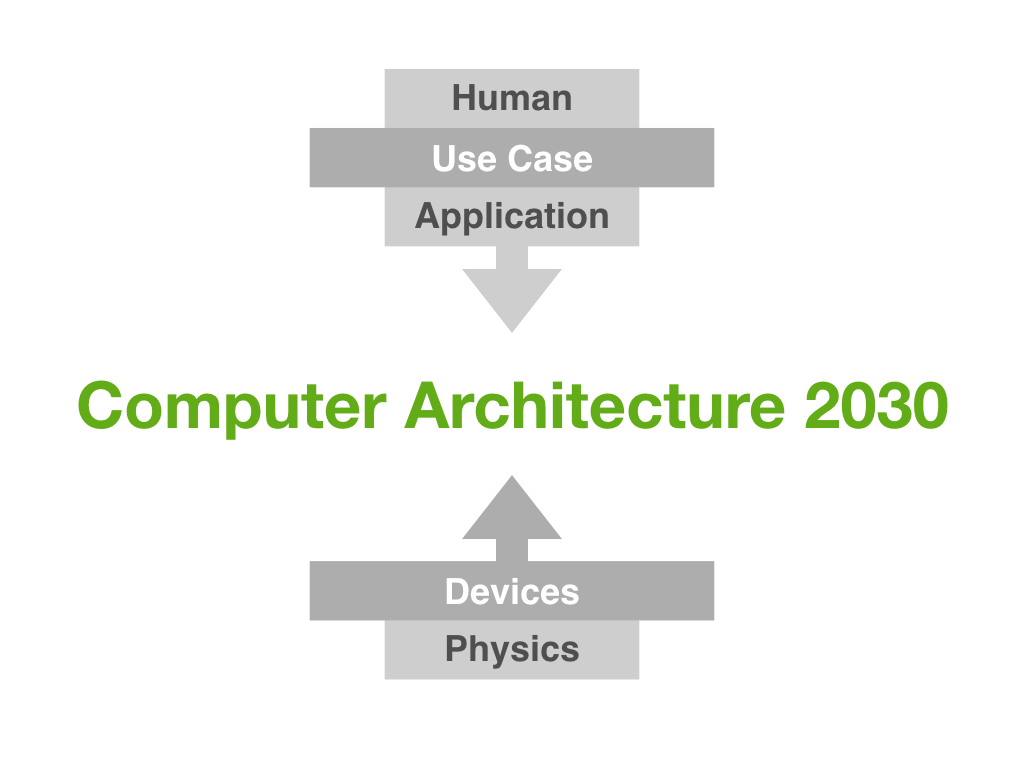

A key theme of these reports was the observation that Dennard Scaling is no longer viable. As a result, architectural innovation, rather than semiconductor technology improvement, will be the key driver of continued advancement in the capability of computer systems. Several years have past since the conclusion of these visioning activities. As we embark upon the post-Dennard era and look towards a post-CMOS life, new themes and priorities are ascendant in the architecture research community. As our field rapidly evolves, we believe it is time to initiate a new community effort to (1) identify the architectural challenges and opportunities of the next fifteen years and (2) reiterate and emphasize the criticality of architecture research to the future of computing to the agencies and companies that support computing research.

The goal of this first Architecture 2030 Workshop is to kick off a new round of visioning activities in a public forum, on where our constituents believe the field is headed, what challenges and opportunities exist, and how we can continue to communicate our impact beyond our discipline. The workshop will be mostly discussion based, with breakout sessions and report-outs. I will also include two keynotes, one on devices and one on applications. Please participate by filling out our survey, which will be used to guide our activities. The workshop will be on Sunday, June 19th.

Agenda for Sunday, June 19

| Time | Event |

|---|---|

| 8:30 | Intro remarks by Luis Ceze and Tom Wenisch (slides) (See also: topic modeling analysis of computer architecture research) |

| 8:50 | Mark Hill (Wisconsin) on “21st Century Computer Architecture” (slides) |

| 9:10 | Tom Conte (GeorgiaTech) on “IEEE Rebooting Computing Initiative & International Roadmap of Devices and Systems” (slides) |

| 9:30 | Devices Keynote: Philip Wong (Stanford) on “Device Technologies for the N3XT 1,000X Improvement in Computing Performance” (slides) |

| 10:30 | Break |

| 11:00 | Steve Keckler (nVidia/UT Austin) on “The Influence of Academic Research on Industry R&D” (slides) |

| 11:25 | Michael Taylor (UCSD) on “Open Source HW: Architecture’s Only Hope for Survival” (slides) |

| 11:45 | Alvy Lebeck (Duke) on “Computing and Biomolecules” (slides) |

| 12:05 | Yuan Xie (UCSB) on “Technology-driven Architecture Innovation: Challenges and Opportunities” (slides) |

| 12:30 | Lunch |

| 2:00 | Applications Keynote: Kayvon Fatahalian (CMU) on “100 Quadrillion Live Pixels: The Challenge of Continuously Interpreting, Organizing, and Generating the World’s Visual Information” (slides) |

| 3:00 | Breakout session kick off |

| 3:30 | Coffee Break |

| 4:00 | Break-out session |

| 5:00 | Report-out/discussion (slides) (video) |

| 5:30 | Wrap-up |

Organizers

- Luis Ceze

- Thomas Wenisch

- Mark Hill (Advisor and CCC Liaison)

- Aasheesh Kolli (UMich), Neha Agarwal (UMich), Amrita Mazumdar (UWash) (Student scribes)

This workshop is supported by the CCC.

Talk abstracts

21st Century Computer Architecture

Mark D. Hill

University of Wisconsin

This talk will briefly review the content, process, and influence of the 2012 CCC white paper that Mark Hill led together with Sarita Adve, Luis Ceze, Mary Jane Irwin, David Kaeli (IEEE TCCA), Margaret Martonosi, Josep Torrellas, Thomas Wenisch, David Wood (ACM SIGARCH), & Katherine Yelick.

Device Technologies for the N3XT 1,000X Improvement in Computing Performance

H.-S. Philip Wong, Department of Electrical Engineering and Stanford SystemX Alliance

Stanford University

21st century information technology (IT) must process, understand, classify, and organize the vast amount of data in real-time. 21st century applications will be dominated by memory-centric computing operating on Tbytes of active data with little data locality. At the same time, massively redundant sensor arrays sampling the world around us will give humans the perception of additional “senses” blurring the boundary between biological, physical, and cyber worlds. Abundant-data processing, which comprises real-time big-data analytics and the processing of perceptual data in wearable devices, clearly demands computation efficiencies well beyond what can be achieved through business as usual.

The key elements of a scalable, fast, and energy-efficient computation platform that may provide another 1,000× in computing performance (energy-execution time product) for future computing workloads are: massive on-chip memory co-located with highly energy-efficient computation, enabled by monolithic 3D integration using ultra-dense and fine-grained massive connectivity. There will be multiple layers of analog and digital memories interleaved with computing logic, sensors, and application-specific devices. We call this technology platform N3XT – Nanoengineered Computing Systems Technology. N3XT will support computing architectures that embrace sparsity, stochasticity, and device variability.

In this talk, I will give an overview of nanoscale memory and logic technologies for implementing N3XT. I will give examples of nanosystems that have been built using these technologies, and provide projections on their eventual performance.

IEEE Rebooting Computing Initiative & International Roadmap of Devices and Systems

Tom Conte

GeorgiaTech

In 2012, IEEE formed a cross-societal initiative, the IEEE Rebooting Computing Initiative (RCI), and tasked it with fundamentally rethinking computing from devices and circuits up through architectures, languages and algorithms: . RCI has held 4 invitation-only summits of thought leaders that have influenced US policy decisions. Starting in 2014, RCI joined forces with the International Technology Roadmap of Semiconductors (also known as “the Semiconductor Roadmap”). In 2016, ITRS moved to IEEE and became the IEEE International Roadmap of Devices and Systems (IRDS). The goal of the IRDS is to roadmap future computing and drive its requirements down to devices to guide the semiconductor industry. I will summarize both the IEEE RCI summits and the IRDS structure and goals.